SLVS-EC Sensor Interface IP for the Next FPGA Generation

The high-speed interface standard SLVS-EC has become an alternative in the choice of standards for high-end/long distance machine vision applications using fast, high-resolution CMOS image sensors. Originally developed by Sony the standard has increasingly gained acceptance among image sensor suppliers and is currently standardized in a working group of the Japan Industrial Imaging Association (JIIA).

SLVS-EC in its latest Release version 2.0 supports higher data rate than v1.2 with a speed increase up to 5Gbps/lane. Compared to other high-speed interfaces in the vision environment from the Rx development environment point of view SLVS-EC has a key advantage in transmission line design and FPGA development since the standard is able to connect to the FPGA transceiver without additional chip. In addition, with the embedded clock lane, no adjustment of skew between the lanes is needed. This facilitates sensor board design to a large extent. SLVS-EC enables correction of transfer errors by using Error Correction Code (ECC) which is particularly suitable for high speed burst mode and long distance transmission.

IPs for Intel, Xilinx and Microsemi-FPGAs

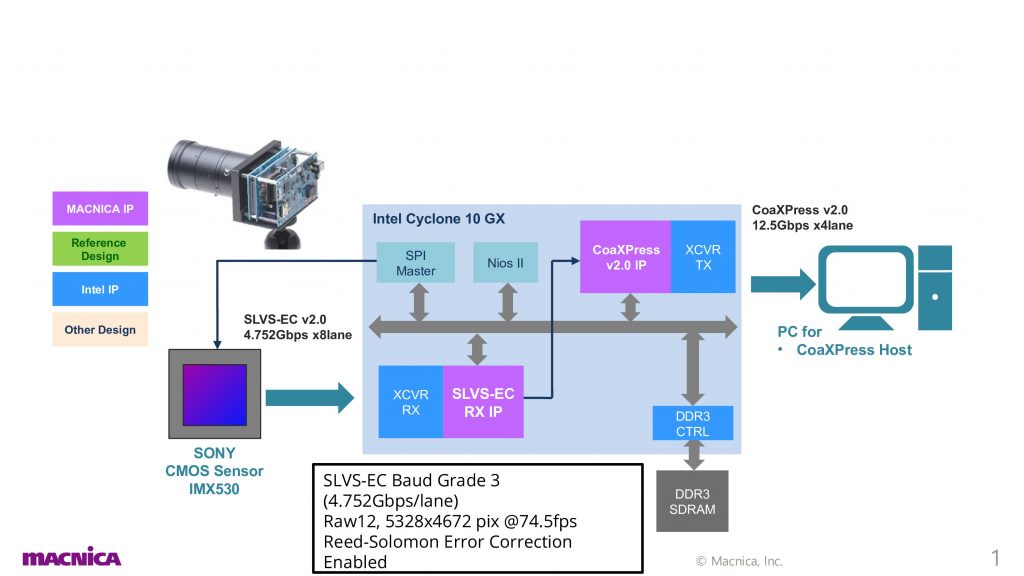

Macnica stands in the tradition of developing machine vision IPs and providing a broad range of board models for the machine vision market to accelerate the adaptation of FPGA technology. The above feature characteristics of the high-speed interface standard SLVS-EC convinced Macnica to develop the sensor interface SLVS-EC Rx IP as an intellectual property toolkit which highly facilitates board-level design for SLVS-EC. Herein, a unique feature of the Macnica IP solution represents the active support of Error Correction Code in the SLVS-EC standard which allows maintaining good image quality even under severe conditions and unexpected data corruption. This SLVS-EC feature to-date is only supported by Macnica IP giving it a stand-alone position in the IP support for the standard. A broad choice of both Intel and Xilinx devices are supported by the SLVS-EC IP. The Intel device families which are supported include Cyclone V GX; Cyclone 10 GX; and Arria 10 GX. In the Xilinx world the supported FPGA families include Artix-7; Kintex-7; Kintex Ultrascale and Kintex Ultrascale+. In addition, since interface transfer rates steadily increase and with that power consumption as well as cooling is becoming a bigger concern Macnica currently develops porting the SLVS-EC IP as well as their CoaXPress IP to the PolarFire FPGA by Microsemi which is now part of Microchip. This low power consumption device would make an EasyMVC PolarFire version quite attractive to machine vision customers. The new IP version targeting the PolarFire FPGA is planned to be released in spring 2021. Most of the introduced devices are compliant with both the SLVS-EC specification versions 1.2 and 2.0.

European IP License and Evaluation Kits

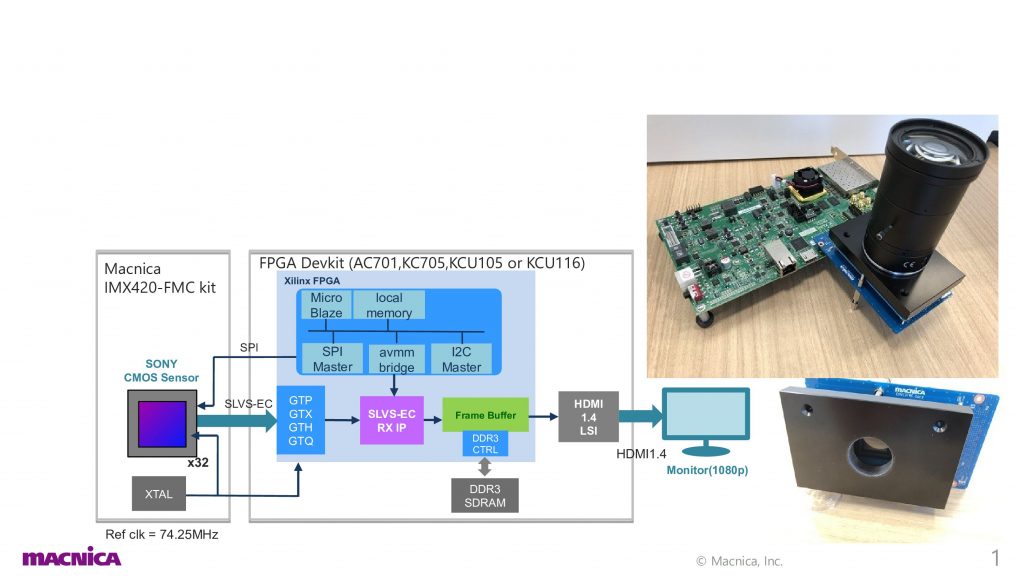

Through the demo environment EasyMVC Macnica offers a versatile machine vision camera development kit. For Macnica SLVS-EC IP demos running on Xilinx devices the Macnica IMX420 FMC kit combined with the Xilinx Development kits AC701; KC705; KCU105; KCU116 can be tested. The choice of EasyMVC combinations for Intel demos includes the sensor boards IMX420/421 or IMX530 together with the FPGA board Cyclone 10GX combined with an interface board which supports HDMI; CoaxPress; USB3; 10Gige or other. For both the Intel and Xilinx version a free evaluation license can be requested for a three month test period. In addition, Macnica ATD Europe can provide a Xilinx Evaluation Kit Kintex UltraScale+ FPGA KCU116 to customers as well as a Macnica EasyMVC IMX420 development kit which both can be loaned free of charge. Furthermore the company is building its own European IP License Agreement to license by themselves IP developed from Macnica, Inc.