Embedded-Designplattform mit SoC-FPGA-Architektur

Kommt bei der Bildverarbeitung KI ins Spiel, muss oft eine leistungsfähige und teure Hardware verwendet werden. Der Ansatz des C-Vision-Kits besteht darin, eine flexible SoC-FPGA-Architektur mit einer performanten Vision Processing Unit (VPU) zu kombinieren und mit industriellen Kameras als Entwicklungsplattform bereitzustellen.

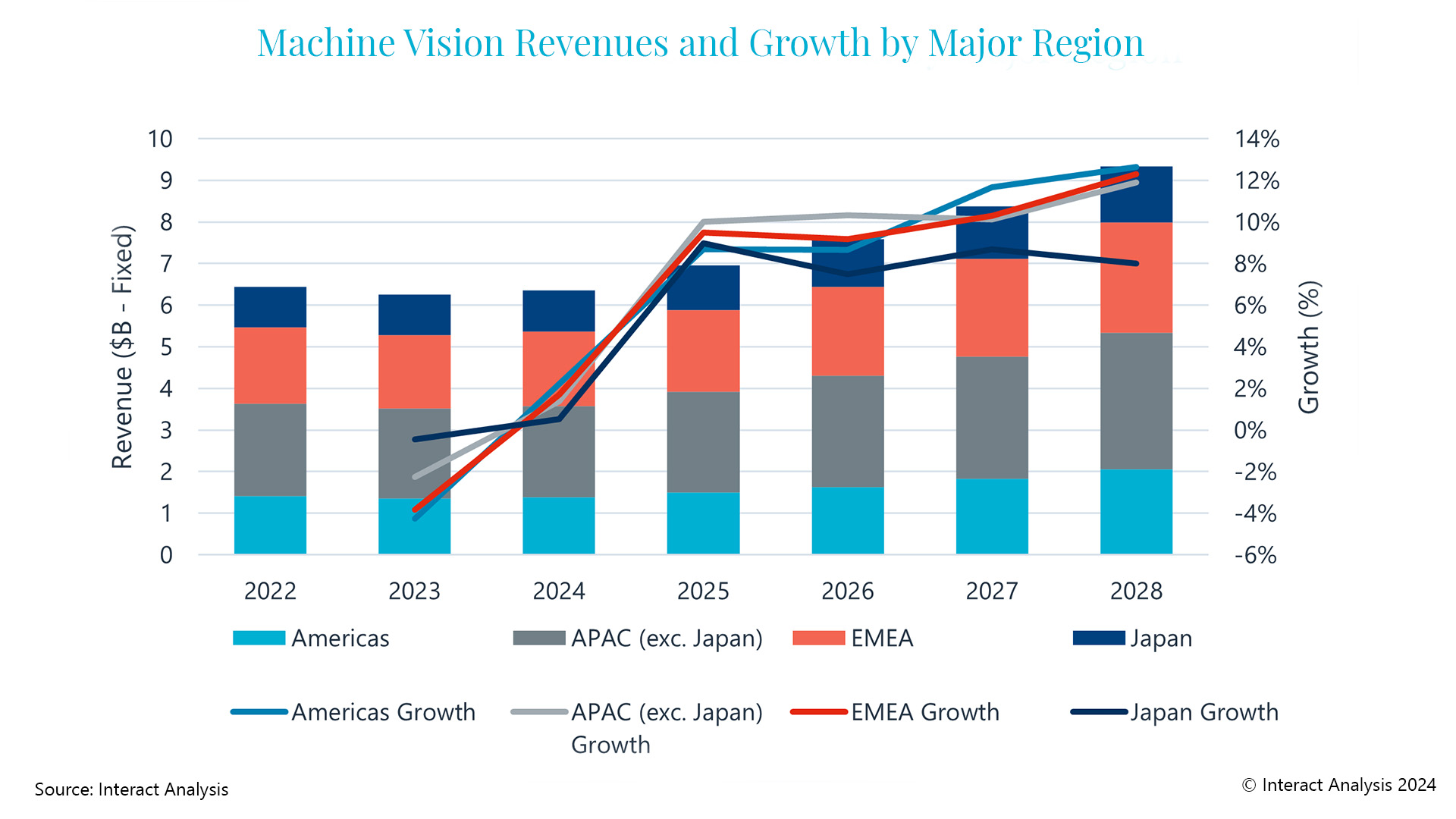

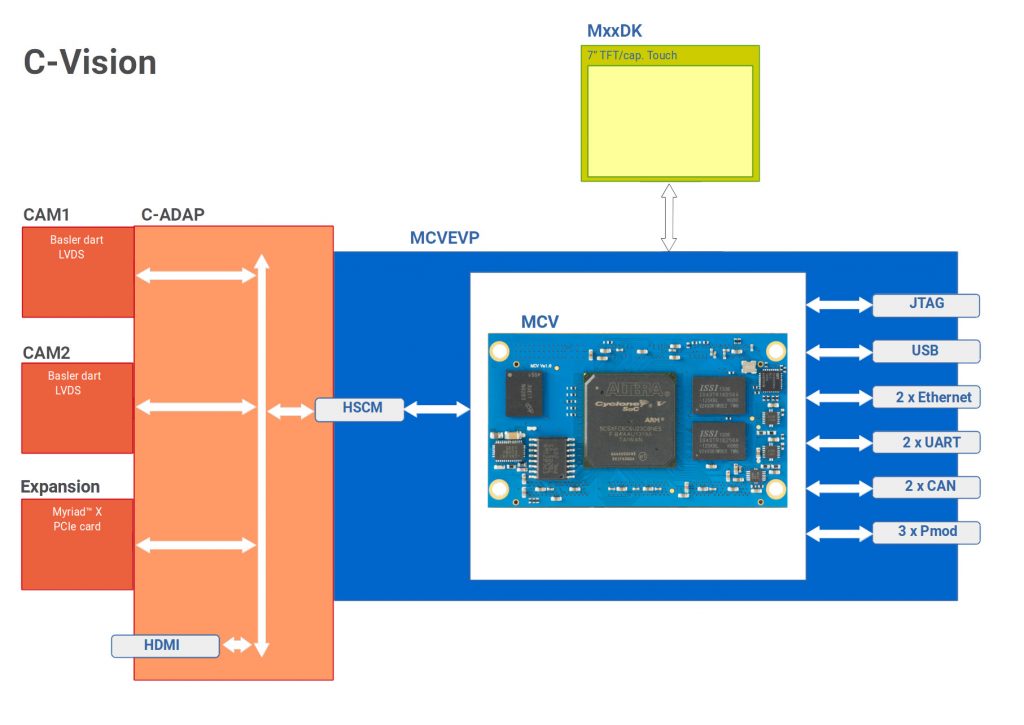

Das C-Vision-Kit ist eine Designplattform für industrielle Anwendungen mit Embedded Vision und künstlicher Intelligenz (KI). Zwei Basler Dart-Kameras (l.o.) werden über das C-Vision-Adapterboard mit dem FPGA-System verbunden. (Bild: Aries Embedded GmbH)

Basis des C-Vision-Kits von Aries Embedded ist das System-on-Module (SoM) MCV, das auf der CycloneV-SoC-FPGA-Architektur von Intel PSG basiert. Für die Verbindung in die Außenwelt wird das SoM auf das MCVEVP-Trägerboard gesteckt. Zwei Basler dart-Kameras werden über das C-Vision-Adapterboard mit dem FPGA-System verbunden. Als Option kann eine mini-PCI-Express Karte zur zusätzlichen Erweiterung der Funktionalität eingesteckt werden. Die Verwendung einer VPU-Beschleunigerkarte mit Intel Movidius Myriad als Referenz ist zudem geplant.

Basis des C-Vision-Kits ist das System-on-Module MCV, das auf der CycloneV-SoC-FPGA-Architektur von Intel PSG basiert. (Bild: Aries Embedded GmbH)

FPGA-Plattformen

Um den steigenden Anforderungen an Bildverarbeitungsanwendungen Rechnung zu tragen, können leistungsfähigere CPU-Architekturen verwendet werden. Diese skalieren über die Taktfrequenz und die Anzahl der verfügbaren Rechenkerne. Alternativ lassen sich FPGA-Plattformen als Rechnerkerne einsetzen, da nicht jede Anwendung die Verwendung von gut ausgestatteten Multicore-Rechnern budgetiert. Dabei wird die Funktionalität von FPGAs durch den Entwickler vorgegeben. Die Implementierung von Kameras und Bildsensoren erfolgt sowohl über klassische Schnittstellen, wie Camera Link, als auch über aktuelle Schnittstellen, wie MIPI-CSI. Mit dem MCV-SoM setzt Aries auf die CycloneV-SoC-FPGA-Architektur von Intel PSG. In diesem Baustein sind zwei ARM-CortexA9-Kerne mit einem FPGA auf einem Chip verbunden. Sie vereinen die Vorteile von Rechnerarchitekturen mit denen von FPGAs. MCV wird durch aktuelle Versionen freier Software, wie U-Boot und Embedded Linux, unterstützt und bietet Yocto und Buildroot als Entwicklungsumgebung für die Softwareentwicklung. Im C-Vision-Kit wird das SoM auf seiner Entwicklungsplattform MCVEVP betrieben. Das Basisboard stellt alle im SoC-FPGA hart codierten Schnittstellen, Ethernet, RS232, CAN und USB auf Steckverbindern bereit, die FPGA -Pins stehen auf Pfostenleisten oder dem HSMC-Stecker, auf dem auch der C-Vision-Adapter steckt, zur Verfügung.

Boardlevel-Kamera & KI-Beschleunigerkarte

Zum Einsatz kommt bei dem Kit auch die Boardlevel-Kameraserie dart von Basler. Die Produktfamilie umfasst zahlreiche Modellvarianten mit Auflösungen von 1.280×960 bis 2.592×1.944 Pixeln und Bildraten von maximal 60fps (bis 160fps für USB3.0). Die Kameras haben einen minimalen Platzbedarf von 27x27mm und stehen mit unterschiedlichen Objektivmounts zur Verfügung. Im C-Vision-Kit lassen sich bis zu zwei dart-Kameras über BCON for LVDS an das FPGA anbinden. Ergänzt wird das Kit zudem mit einer KI-Beschleunigerkarte, die in den miniPCI-Express-Slot des C-Vision-Adapterboards eingesteckt wird. Die Karte basiert auf der Movidius Myriad X VPU von Intel. Neben den dedizierten Vision-Funktionen verfügt diese über eine komplett einstellbare ISP-Pipeline für anspruchsvollste Bild- und Videoanwendungen. Sie unterstützt die hardwarebasierte Codierung für Videoauflösungen von bis zu 4K. Sie verfügt über einen Neural Compute Engine, sowie über einen dedizierten Hardware-Beschleuniger, um tiefe neuronale Netzwerkanwendungen auf dem System auszuführen. Softwareseitig wird die Beschleunigerkarte durch das OpenVino Toolkit von Intel unterstützt. Dieses kann plattformübergreifend auf verschiedenen Host-Betriebssystemen eingesetzt werden und besteht aus dem Deep Learning Deployment Toolkit (Modelloptimierer und Inferenzmaschine), optimierten Funktionen für OpenCV/OpenVX sowie über 15 Beispielcodes und vortrainierte Modelle. Training bedeutet in diesem Kontext, dass das System aus vorhandenen Daten lernt bzw. die Daten neu angelernt/erfasst, werden.