Vereinfachter Anschluss

Schnellere FPGA Anbindung für neue Sony CMOS Sensoren

Mit dem integrierbaren IP-Core für Sonys neue CMOS Global-Shutter-Bildsensoren der dritten Generation mit SLVS-EC-Schnittstelle profitieren Anwender von einer verkürzten Time-to-Market und einer verbesserten Performance für die Vision-Entwicklung mit FPGAs von Xilinx.

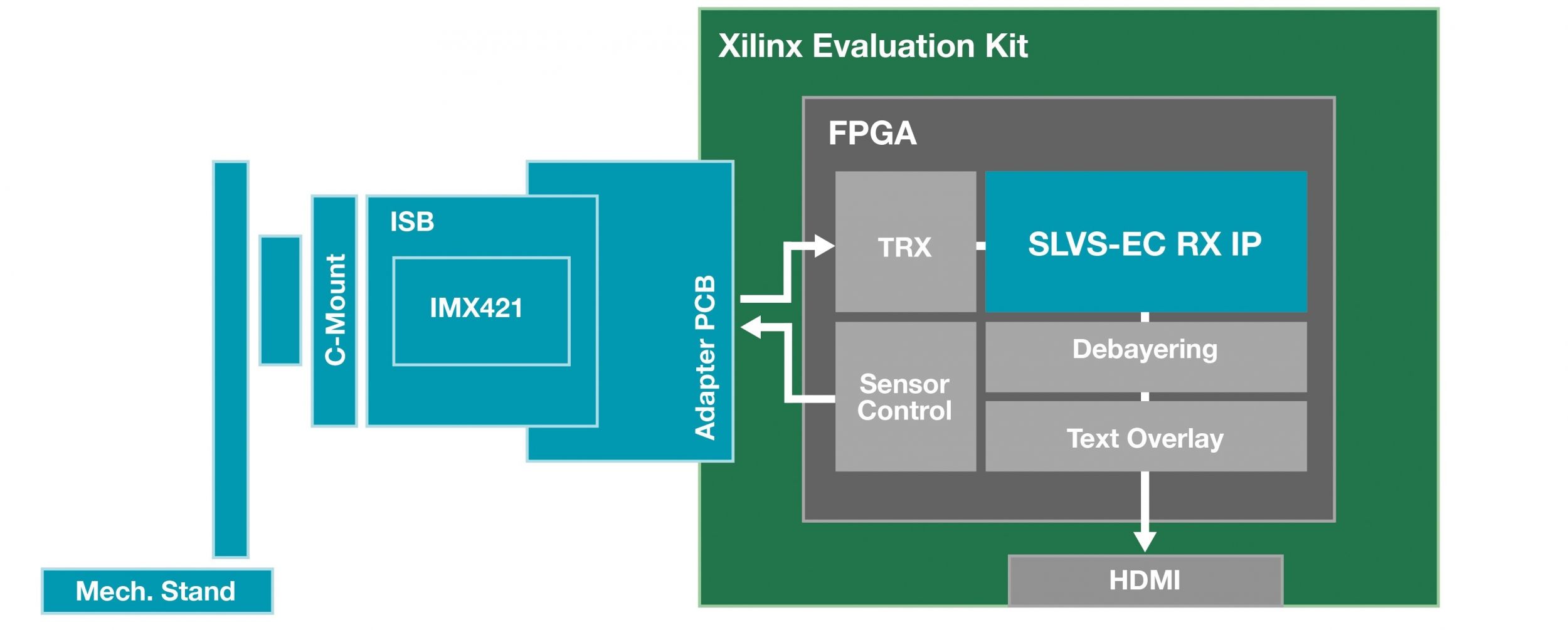

Bild 1 | Der SLVS-EC IP-Core erleichtert Anwendern die Verbindung zwischen Image Sensor und FPGA. (Bild: Framos GmbH)

Der SLVS-EC-Schnittstellenstandard von Sony wird als Hochgeschwindigkeitsschnittstelle der neuesten Bildsensoren eingesetzt und erlaubt einen höheren Durchsatz, eine bessere Signalintegrität sowie einfachere Designs. Entwickler, die an Lösungen mit Xilinx-FPGAs und SoCs arbeiten, können den SLVS-EC RX IP Core und das Evaluation Board von Framos sowie dezidierte Quellcodebeispiele nutzen. Die Innovationen der neuen Pregius-Bildsensoren der dritten Generation basieren vor allem auf deren Bildqualität und Geschwindigkeit. Angesichts der zahlreichen Qualitätsverbesserungen und der damit erreichten Sensorleistung ist allerdings eine Übertragung der Bilddaten, bei gleichzeitiger Steigerung der Übertragungsgeschwindigkeit, mit den bisherigen Sensorschnittstellen nicht möglich.

Acht Lanes mit je 2,376Gbps

Mit bis zu acht Lanes, die jeweils 2,376Gbps bieten, steht mit SLVS-EC (Scalable Low-Voltage Signaling with Embedded Clock) eine neue Sensorschnittstelle zur Verfügung, die den Anforderungen der Industrie hinsichtlich Auflösung und Geschwindigkeit gerecht wird. Die Ausgabegeschwindigkeit wurde gegenüber der zweiten CMOS-Generation von Sony auf 18,4Gbps fast verdoppelt. Es stehen damit mehr als dreimal höhere Bandbreiten pro Lane und höhere Auflösungen zur Verfügung, sowie ein einfacheres Systemdesign gegenüber den gängigen SubLVDS-Schnittstellen. Mit SLVS-EC können Anwender von schnelleren und leistungsfähigeren Sensoren sowie größeren Kabellängen, oder – wenn sie weniger Lanes nutzen – von einem vereinfachten und damit kleineren Hardwaredesign profitieren. Mit ihrer integrierten Taktung (Embedded Clock) ist die Schnittstelle robust gegenüber Taktversätzen, was eine höhere Bandbreite ermöglicht und dedizierte Clock-Lanes überflüssig macht.

Bild 2 | Schema eines Kameradesigns mit einem Sensorauswertungs-Erweiterungspaket für ein Xilinx Ultrascale Evaluation-Board. (Bild: Framos GmbH)

Verbindung IP-Core mit FPGA

Um die neuen Bildsensoren mit einer leistungsfähigen Onboard-Verarbeitung zu kombinieren, sind für die FPGAs aber Spezialkenntnisse und erfahrene Entwickler vonnöten. Darüber hinaus bedeutet die komplexere SLVS-EC-Schnittstelle aufgrund der erforderlichen Byte-zu-Pixel-Konvertierung und korrekten Transceiver-Konfiguration einen höheren Aufwand und einen größeren Overhead für die allgemeine Sensorimplementierung. Die meisten Anwender fokussieren sich allerdings auf ihre Core-Spezialisierung bzw. USP-Anwendung und müssen die Entwicklungszyklen kurzhalten. Um diese Ziele zu erreichen, stehen ihnen nun hilfreiche Entwicklungswerkzeuge und SDKs zur Verfügung.

Spezielle IP-Cores haben die Aufgabe, die Signalumwandlung innerhalb des FPGA oder SoC zu übernehmen, indem sie die Sensordaten auf einer gut dokumentierten Schnittstelle empfangen und einen vorentwickelten Logikblock bereitstellen. Der SLVS-EC RX IP Core für Xilinx-FPGAs und SoCs ist eine bewährte Implementierung von SLVS-EC als Sonys bevorzugter Schnittstelle für deren Bildsensoren. Als On-Chip-Funktionsblock verbindet der IP Core die FPGA-Logik mit dem Datenstrom des Bildsensors, nimmt die Schnittstellendaten an und verwaltet die Byte-zu-Pixel-Konvertierung für alle verfügbaren Lane-Konfigurationen. Er bereitet damit einen optimalen und effizienten Verarbeitungsablauf auf dem FPGA vor. Die Software unterstützt SLVS-EC v1.2 mit 1, 2, 4 oder 8 vom Nutzer konfigurierbaren Lanes und liefert Pixelformate zwischen 8 und 14Bit als Rohdaten. Der IP Core unterstützt dynamische Modusänderungen sowie eine AXI4-Kommunikations- und Control-Schnittstelle. Vorimplementierte IPC Cores, die Anwender bei der Erreichung ihrer Ziele unterstützen, werden als Pakete angeboten, die sowohl Konstruktionsdateien, eine Simulationsumgebung (z.B. ModelSim) und als Referenz dienende Implementierungsbeispiele umfassen. Das dazugehörige EVB-Kit bietet Beispiele und Designs, die beim Implementieren und Testen eines SLVS-EC-basierten Sensors unterstützen (inkl. Hard- und Softwareumgebung), sowie dokumentierte Implementierungsbeispiele mit Quellcodes.