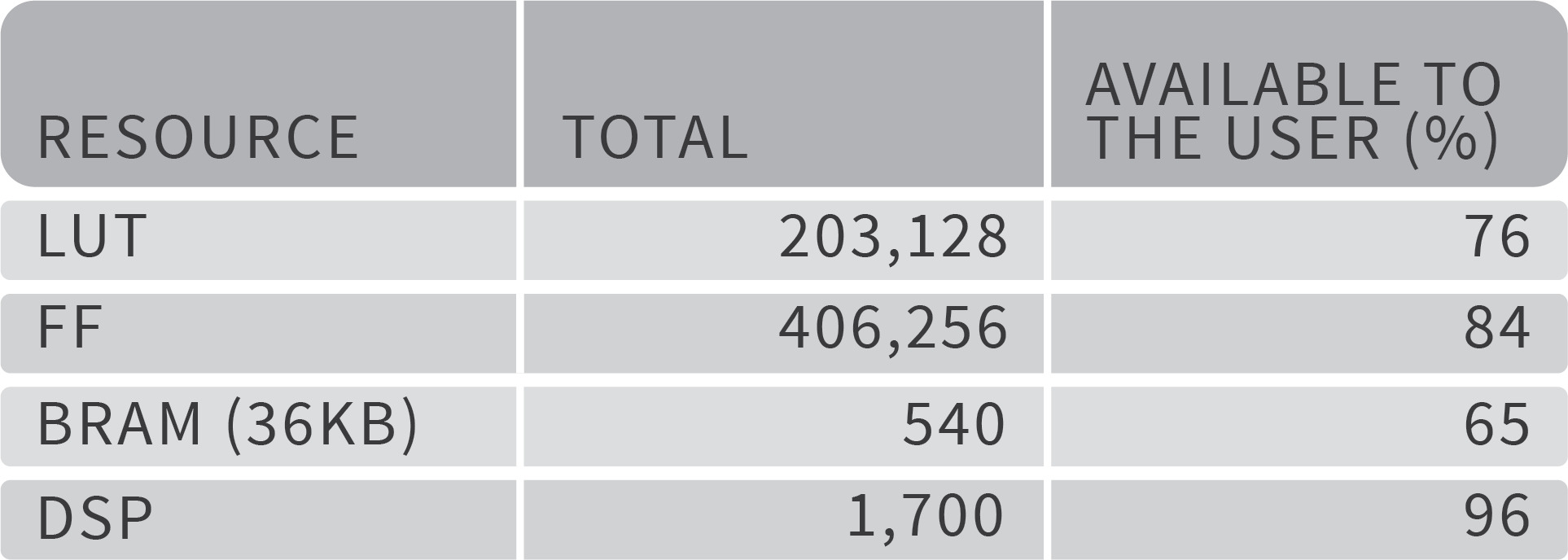

Das CustomLogic-FPGA-Design belässt bis zu 70 Prozent der Ressourcen auf den Xilinx Kintex Ultrascale XCKU035 FPGAs. (Bild: Euresys s.a.)

FPGA-Design-Kit

Das CustomLogic-FPGA-Design belässt bis zu 70 Prozent der Ressourcen auf den Xilinx Kintex Ultrascale XCKU035 FPGAs, die in den Framegrabbern Coaxlink Octo und Coaxlink Quad CXP-12 verwendet werden. Das Design-Kit bietet zudem Zugriff auf den Pixelfluss der CXP-Kamera, DDR4 On-Board-Speicher und PCIe Gen3-Konnektivität. In der Designphase werden dabei die Vivado-Entwicklungstools von Xilinx verwendet. Das Design-Kit wird mit einem Referenzdesign geliefert, das ein Vivado-Projekt mit allen für den Nutzer verfügbaren Schnittstellen enthält. Die Schnittstelle für den Datenstrom (Pixel) basiert auf dem AMBA AXI4-Stream-Protokoll. Quellseitig bietet die Schnittstelle von der Kamera erfasste Bilder und überträgt die Nachbearbeitung von der Benutzerlogik an den PCI-Express-DMA-Backend-Kanal. Die Schnittstelle für Steuerung/Status ermöglicht dem Anwender, die Register in der Benutzerlogik über die Coaxlink-Treiber-API zu lesen und zu schreiben. Die Ereignisschnittstelle liefert der Benutzerlogik, zeitgestempelte Ereignisse an das Memento Logging-Tool mit einer Genauigkeit von 1/s. Memento bietet Entwicklern so eine präzise Zeitachse der Ereignisse mit Kontextinformationen einer Logikanalysatoransicht. Es bietet wertvolle Hilfe bei der Anwendungsentwicklung und beim Debuggen, sowie während des laufenden Maschinenbetriebs. Die Vivado High-Level Synthesis (HLS), die als kostenloses Upgrade in allen Vivado HLx-Editionen enthalten ist, beschleunigt die IP-Erstellung durch die Möglichkeit von Spezifikationen in C, C++ und SystemC, die direkt in programmierbare Xilinx-Geräte implementiert werden können. Dazu ist keine manuelle Erstellung von RTL-Code (Register Transfer Level) erforderlich. Für das FPGA-Design müssen allerdings die Einschränkungen und Begrenzungen von FPGAs bekannt sein. Darüber hinaus sind Programmierkenntnisse in C++ erforderlich. So schließen z.B. die RAM-Begrenzungen in FPGAs in der Regel eine Speicherzuweisung aus.

Fazit

CustomLogic kann viele Bildverarbeitungsaufgaben parallel ausführen und Pixel direkt ohne Pufferung oder Latenz verarbeiten. Durch die Verlagerung sich wiederholender und massiv parallel ausgeführter Aufgaben auf das FPGA kann sich die CPU auf High-Level-Aufgaben konzentrieren. Das in dem FPGA-Design-Kit enthaltene geistige Eigentum, sowie die CoaXPress-Schnittstelle und das Logging-System Memento helfen dabei, Produkte deutlich schneller als bisher auf den Markt zu bringen.