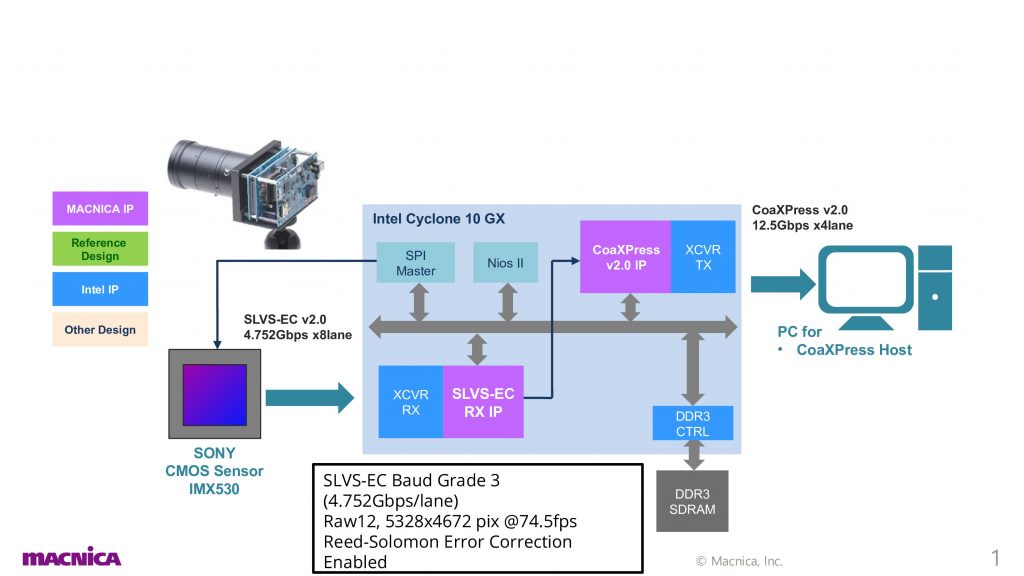

SLVS-EC Sensor Interface IP for the Next FPGA Generation

The high-speed interface standard SLVS-EC has become an alternative in the choice of standards for high-end/long distance machine vision applications using fast, high-resolution CMOS image sensors. Originally developed by Sony the standard has increasingly gained acceptance among image sensor suppliers and is currently standardized in a working group of the Japan Industrial Imaging Association (JIIA).

SLVS-EC in its latest Release version 2.0 supports higher data rate than v1.2 with a speed increase up to 5Gbps/lane. Compared to other high-speed interfaces in the vision environment from the Rx development environment point of view SLVS-EC has a key advantage in transmission line design and FPGA development since the standard is able to connect to the FPGA transceiver without additional chip. In addition, with the embedded clock lane, no adjustment of skew between the lanes is needed. This facilitates sensor board design to a large extent. SLVS-EC enables correction of transfer errors by using Error Correction Code (ECC) which is particularly suitable for high speed burst mode and long distance transmission.