Edge-Applikationen haben zahlreiche Herausforderungen. Dabei geht es um Schnittstellen zu Sensoren, Aktoren, Displays, sowie zum System. Flexibilität für verschiedene, aktuelle und neue Sensoren einerseits, Kompatibilität zum bestehenden System andererseits. Es geht aber auch um die optimale Balance zwischen Performance und Verlustleistung, zentraler und dezentraler Datenverarbeitung, Verfügbarkeit und Bandbreite der Schnittstellen, Baugröße und Kosten. In Kameras hat sich der Einsatz von FPGAs bewährt, die sowohl mit LVDS als auch mit MIPI CSI-2 umgehen können, und Skalierbarkeit bezüglich der aufgeführten Attribute mitbringen. Aber mit den Anforderungen an die Edge-Komponente von einer Produktgeneration zur nächsten steigen auch die Anforderungen an ein FPGA. Aus dem Vollen schöpfen ist wegen der Kosten und der Verlustleistung kaum möglich, also schauen Systemarchitekten ständig nach dem optimalen Mix aus verlustleistungsarmen FPGAs, sowie Soft- und Hard-IP für die notwendige Funktion und Leistungsfähigkeit. Aus dieser Perspektive ist die aktuelle und zukünftige Entwicklung der Titanium FPGA-Familie von Efinix interessant.

FPGAs mit bis zu 60k Logikelementen

Nach der Einführung der Trion-FPGA-Familie von Efinix, die in vielen Produkten bereits eingesetzt wird, bringt die Titanium-Familie mehr Features, größere Komplexität – weiterhin mit dem Fokus auf geringe Verlustleistung und kleine Baugrößen. Zum Beispiel sind MIPI CSI-2 Receiver und Transmitter im Trion als Hard-IP – also festverdrahtet – vorhanden und unterstützten bis zu 1,5Gbit/s pro MIPI-Lane. Die gleiche Geschwindigkeit kann im Titanium bereits mit einer Soft-IP-Lösung über schnelle IO-Zellen abgebildet werden.

Die ersten Titanium-FPGAs, mit bis zu 60k Logikelementen und geringem Strombedarf, sind ebenfalls schon geraume Zeit in Produktion. Mit Gehäuseabmessungen des Ti60 ab 3,5×3,4mm oder des Ti60-SiP mit 5,5×5,5mm ermöglichen sie eine effiziente Miniaturisierung. SiP bedeutet in diesem Fall, das man ein FPGA mit 60k Logikelementen, 256 Mbit HyperRAM und SPI-Flash, LVDS und MIPI-Unterstützung, in einem Gehäuse erhält.

In der nächsten Ausbaustufe stehen Titanium Ti90 bis Ti180 weiterhin für geringe Verlustleistung, bieten aber zusätzlich zur dreifachen Logik-Kapazität und den schnellen digitalen Ein- und Ausgängen bis zu vier MIPI-DPHY-Receiver und -Transmitter als Hard-IP. Die maximale Geschwindigkeit steigt hier auf 2,5Gbit/s pro Lane. Gehäuseabmessungen von 13×13 bis 19x19mm lassen ebenfalls ein Produktdesign mit kleinen Baugrößen zu. Mit der Anzahl der Schnittstellen und zunehmenden Datenraten wird allerdings die Anbindung eines schnellen externen Speichers für viele Applikationen zwingend. Titanium antwortet darauf mit einem festverdrahteten Controller für LPDDR4/X Speicherbausteine, sowie schnellen und zahlreichen DSP-Blöcken, so dass Daten nicht nur zwischengespeichert sondern insbesondere (vor)verarbeitet werden können.

Ausrichtung auf VisionApplikationen

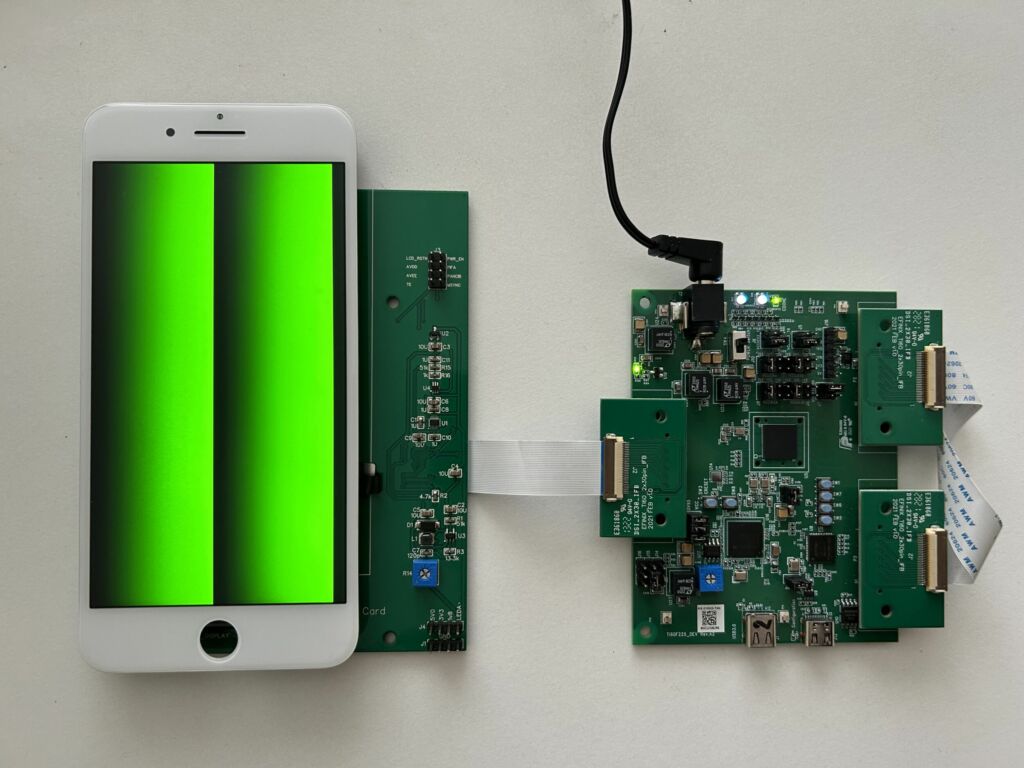

Die Ausrichtung der aktuellen Titanium-Familie nicht nur, aber insbesondere auf Vision-Applikationen, ist auch am Funktions- und Lieferumfang der Development Kits zu erkennen. Integrierte MIPI-DPHYs sind über Stecker zugänglich, an welche eine mitgelieferte Kamera oder ein Display angesteckt werden kann. Mit der Out-of-the-Box-Demo (OoB-Demo), die auf jedem Kit vorprogrammiert ist, und die über die Support-Seiten als FPGA-Projekt heruntergeladen werden kann, läuft innerhalb kurzer Zeit nach der Inbetriebnahme das erste Kamerabild über das MIPI-DSI-Display des Ti60 oder den HDMI-Monitor am Ti180 Development Kit. Die in den Kits enthaltenen Komponenten – beispielsweise eine RaspberryPi-Kamera – sind günstig und für Erweiterungen leicht zu beschaffen. So kann die Ti180-OoB-Demo bei Bedarf mit weiteren Kameras versehen werden. Die Demo erkennt bis zu vier Kameras und gibt die Videos wahlweise einzeln oder in einem viergeteilten Bild wieder.

Konfigurierbarer IP-Core mit 300MHz

Zentrale Komponente vieler Projekte und Demo-Designs ist ein RISC-V-Prozessor, den Efinix unter der Bezeichnung Sapphire SoC als konfigurierbaren IP-Core in der Efinity-Software bereitstellt. Die Bandbreite der RISC-V-Konfigurationen reicht vom kleinen Mikrocontroller mit FPGA-internem RAM, SPI, UART, GPIO bis zum Linux-fähigen Multicore-RISC-V mit FPU, MMU und LPDDR4-Memory-Controller. Obwohl Sapphire ein Soft-IP ist – also zusammen mit dem Anwender-Design synthetisiert und im programmierbaren FPGA-Kern implementiert wird, sind je nach RISC-V-Konfiguration Taktraten weit über 300MHz möglich.